|

���R�Ɋǐڑ�(Ver.1) 50BM8 �V���O���E�A���v ����3���@�@����2�̒ǎ��E���v���G�� |

Ver.01 2015/12/7

|

����3���@�́A�㞊����������L���ɂ����u����2 ���i���J�X�R�[�h���v�̒ǎ��ł��B �����u����2 ���i���J�X�R�[�h���v�́A�����L���ɂ��ƁA���i���J�X�R�[�h��H�ɂ��Ē�d���������߁A�܂��A���i�����f�q���g�����W�X�^�[����J-FET�ɕύX���ĉ�H���V���v���ɂ�������A�Ƃ̂��Ƃł��B�����āA���̉����ɂ���c���m�C�Y�� 98��V�ɂ܂ʼn��P���������ł��B

�@ |

|

��@�����O�ɍl����

���́A�d����H���烊�v���t�B���^�[��H���ȗ��ł���̂��A�f�l�ڂɂ͂ƂĂ��s�v�c�ł��B �����āA���́A���i��H�́u��d���������߂�v�����ŁA�c���G��������ɒቺ����̂ł��傤���H

�������̉���L���ɂ��A�o�͊�V2�̃J�\�[�h��B�d�����������R���f���T�[�i���j�ɂ��̔閧�����邻���ł��B���̔閧�̒��g��m�肽���āA�邯����́w�^��ǃA���v�̑f�x��136�ł���141�ł�ǂ݂Ȃ���A��H���g���[�X���܂����B�ȉ��A���Ȃ�ɗ������������̂܂Ƃ߂ł��B�i����A�ȉ������邩���j

���F���̃R���f���T�[�̉�H�`�Ԃ́A�~�j���b�^�[�ł�����݂́u�V���[�g���[�v�E�R���f���T�[�v�Ɠ����`�Ԃł��B�ȍ~�A���̃R���f���T�[���u�V���[�g���[�v�E�R���f���T�[�v�ƋL���܂��B

|

|

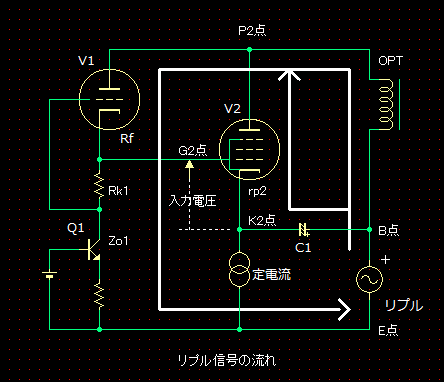

��@���v���M���̈ꎟ�d���̗���Ɠd���l B�d���̎c�����v�����X�s�[�J����o�͂���郋�[�g�Ƃ��ẮA �@�o�̓g�����X��1�����ɒ��ڗ���郋�[�g �A�o�͊�V2�ɂ�葝������郋�[�g ������܂��B �����āA�{��H�ł͂��܂�e���͖��������̂ł����A�@�ƇA�͋t���ł��B �����̂��Ƃ��ӎ����Ȃ���g���[�X���܂��B

�E�}���g���[�X������H�ł��B�o�̓g�����X��1�����ɒ��ڗ���郊�v���M���ƁA�o�͊�V2�ɓ��͂����܂ł̃��v���M���̗���i���v���M���̈ꎟ�d���j�����Ă݂܂����B�o�͊�V2�ɂ�葝�����ꂽ���v���M���͋L���Ă��܂���B

���̃��v���M���̈ꎟ�d���̗��������ƁA�V���[�g���[�v�E�R���f���T�[C1�𗬂�郋�[�g�́AC1�̌𗬃C���s�[�_���X���ƂĂ��Ⴂ�̂��o�͊�V2�̃J�\�[�h�iK2�_�j�ɂ̓��v���������������̂܂܌���܂��B���̂��߁A�o�̓g�����X��1�����ɒ��ڗ���郊�v���M���̃��[�g�́A�ʏ�̑�����H�ƈ���Ă��āA���v���M����OPT����o�͊�V2���ɂ͗���܂���B |

|

|

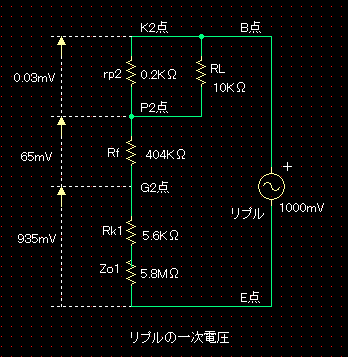

���}�́A�e�f�q���R��ɒu�������āAC1��Z�������}�ŁA���v���d�������u����1000mV�Ƃ��Ă��܂��BZo1�͏��i��H�̏o�̓C���s�[�_���X��5.8M���ARf�͋A�Ҋ�V1���R��ƌ��Ȃ����Ƃ��̒�R��404K���A�܂��Arp2��V2�̓�����R��0.2K���ł��B

|

|

|

|

�� �E���i��H�̏o�̓C���s�[�_���X�@5.8M�� �|2SA1775A�̊ȈՃ��f������菉�i��H���V�~�����[�V�������ċ��߂��l �E�o�͊�V2�̓�����R�@0.2K�� �@�|P-G�A�Ҍ�̒l�A�u������R�ƃ_���s���O�E�t�@�N�^�[�v���Q�� |

|

�@�@�o�̓g�����X��1�����ɒ��ڗ���郋�[�g �o�̓g�����X��1�����ɒ��ڗ���郊�v���M���́AOPT1����(10K��)��V2�̓�����R(0.2K��)�̕�����R�l���A0.2K��=10K��//0.2K�� �Ȃ̂ŁA0.03mV�ł��B OPT��1�����̓��͓d����0.03mV�̂Ƃ��A2�����̏o�͓d���́AOPT�̃C���s�[�_���X�䂩��v�Z����ƁA1��V�i>0.03mV��0.028�j�ɂ������Ȃ��l�ł��B

�A�o�͊�V2�ɂ�葝������郋�[�g ���i��H�̏o�̓C���s�[�_���XZo1���ƂĂ��傫�����Ƃ���A�o�͊�V2�̃O���b�h�iG2�_�|E�_�ԁj�Ɍ���郊�v���M����935��V���Ȃ�܂��B�ʏ�̉�H�ł��ƁA����935mV�����̂܂o�͊�V2�ő�������邱�ƂɂȂ�܂��B�������A�V���[�g���[�v�E�R���f���T�[C1�ɂ��A�o�͊�V2�̃J�\�[�h�ɂ̓��v���M��1000mV�����̂܂܌����̂ŁiK2�_��B�_�����d�ʁj�A�����́|65mV�iG2�_-K�_�ԁj�������A�o�͊�V2�ő�������邱�ƂɂȂ�܂��B

|

|

|

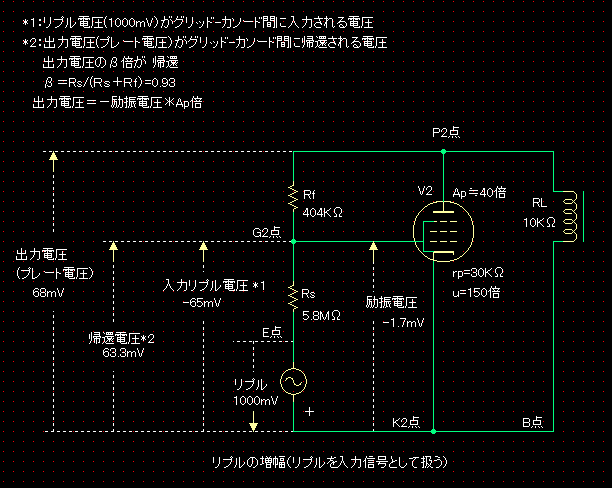

���́|65mV�́A�ǂ̒��x��������ďo�͊�V2�̃v���[�g�Ɍ����̂ł��傤���H�@�g�[��P-G�A�ҁh�ɂ��A���܂葝������Ȃ��Ǝv���̂ł����B

�v�Z����ƁA�o�͊�V2�̃O���b�h����v���[�g�܂ł̑���������}40�{�ŁA�v���[�g����O���b�h�ɖ߂����A�ғd����0.93�{��5.8M��/(5.8M��+404K��)�Ȃ̂ŁA�v���[�g�Ɍ����o�͓d���́A68mV�ƂȂ�܂��B �E�i���͓d���{�A�ғd���j��40�{���|�o�͓d�� �E�A�ғd�����o�͓d����5.8M��/(5.8M��+404K��) �|65mV���͂�68mV�o�́A�������͂ق�1�{�i�������ĂȂ��I�I�j

�t���̏o�̓g�����X��1�����ɒ��ڗ���郊�v���M����0.03mV�ł����̂ŁA����68��V�����̂܂�OPT��1�����Ɉ������܂��B�����āAOPT��2�����Ɍ����c���G���́AOPT�̃C���s�[�_���X��i10K���F8���j��OPT�̓d�͑����i�����0.9�{�j���狁�߂�ƁA1.7mV��65mV����(8��/10K��)��0.9�{ �ł��B

���ۂ̐�������̎c�����v���d����660mV�ł����̂ŁA�X�s�[�J�[�q�Ɍ����c�����v���́A 1.1mV��660mV��1.7mV/1000��V �ƂȂ�͂��ł��B �@ |

|

|

☞�@�c���G���̎����l�́A0.9��V�`0.8mV�ł����̂ŁA�v�Z�l1.1mV����߂ɂȂ�܂����B����́A�c���G���̑唼���c�����v���ɂ��G���������Ƃ���A�V�~�����[�V�����ŋ��߂����i��H�̏o�̓C���s�[�_���X�l��5.8M�����A���ۂ́A�����Ƒ傫�Ȓl�������Ɛ������܂����B�i����8M���`9M�����炢�Ȃ�A�c�����v���̎G���ʂ�0.9mV�`0.8mV�ƌv�Z����܂��B��������2SC1775A�̃f�o�C�X���f������������������I�H�j

☞�@��40�{����������������1�{�ɂȂ��Ă��܂��B�@�g�[��P-G�A�ҁh�� �g�[���h���āA�����䂤���ƂȂ̂ł��ˁB

|

|

|

��@���́A���i��H�̒�d���������߂�Ɖ��P�����̂��H ���_�I�ɂ́AV2�̃O���b�h�ƃJ�\�[�h�����d�ʂɂȂ�A��������郊�v���M���̓[���ł��B�J�\�[�h���̃��v���d���͌������Ȃ��̂ŁA��������郊�v���M�������Ȃ������Ƃ��ẮA �@ ���i��H�̏o�̓C���s�[�_���X���グ��i��d���������߂�j �A �A�Ҋ�V1�̒�R�l�������� ���l�����܂��B ����̉���2�́A���i���J�X�R�[�h�����邱�ƂŇ@�����������Ă���A�Ɨ������܂����B

|

|

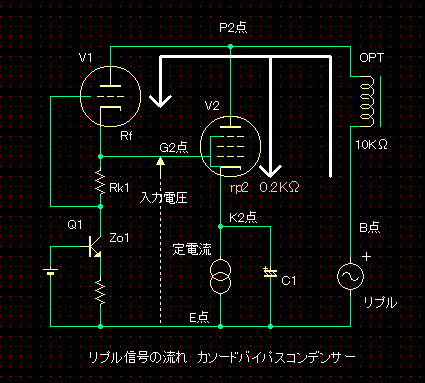

��@�@�~�j�����@�J�\�[�h�o�C�p�X�E�R���f���T�[�ɕύX �o�͊�V2�̃J�\�[�h�ɓ����Ă����V���[�g���[�v�E�R���f���T�[C1���A�J�\�[�h�ƃA�[�X�Ԃɐڑ������ʏ���J�\�[�h�o�C�p�X�E�R���f���T�[�������Ƃ��܂��B ��Ɠ��l�ɁA���̂Ƃ��̃��v���̗�����l����ƁA���x�́A����OPT��1�����𗬂�郊�v���M���́A�o�͊�V2���ɗ���邱�ƂɂȂ�܂��B OPT1�����C���s�[�_���X10K���Ɣ�ׂďo�͊�V2�̓�����R��0.2K���ƈ��|�I�ɏ������̂ŁA�c�����v���d�����قƂ�ǂ��̂܂�OPT��1�����Ɍ�������ƂɂȂ�܂��B�܂��A�t���̑�������郊�v���M���́A���i�̏o�̓C���s�[�_���X�������Ă��o�͊�V2�̓�����R�̖�200��������ɂȂ�̂ŁA�ƂĂ��������Ȃ�܂��B �]���āA���v���G�����h���Ƒ��������Ƃ��\�z����܂��B

���ۂɁA����1���@�Ő}�̂悤��C2���J�\�[�h�o�C�p�X�E�R���f���T�[�Ƃ�������������Ƃ���A1mV����Ă����c���G����19��V�I�ƂȂ�A���p�ɑς��Ȃ��A���v�ɂȂ��Ă��܂��܂����B �@�@ |

|

�o�͊�V2�̃J�\�[�h��B�d�����������V���[�g���[�v�E�R���f���T�[�A���܂��ł��Ă��܂��˂��B�@�������I �@ |

�@

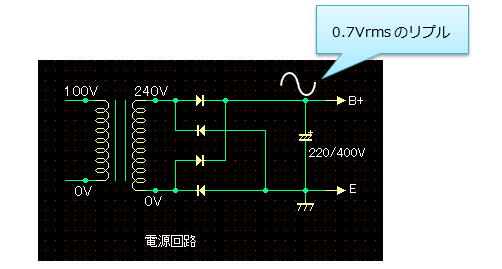

���������A����{�Ƃ����d����H�i�E�}�j�ɂ̓��v���t�B���^�[�̉�H������܂���B������

���������A����{�Ƃ����d����H�i�E�}�j�ɂ̓��v���t�B���^�[�̉�H������܂���B������